PCIe Standards: What You Need to Know

PCIe is a core technology used in many types of computer servers and endpoint devices. PCIe is scalable, and slots come in different configurations of bidirectional lanes: x1, x4, x8, x16, x32. The number represents the number of lanes in the PCIe slot. For example, a PCIe x1 slot provides one lane and transmits data at 1 bit per cycle. A PCIe x2 slot provides two lanes and transmits data at 2 bits per cycle, and so on. PCIe cards fit interchangeably into slots, but the bandwidth available depends upon the version of the PCIe standard of the card.

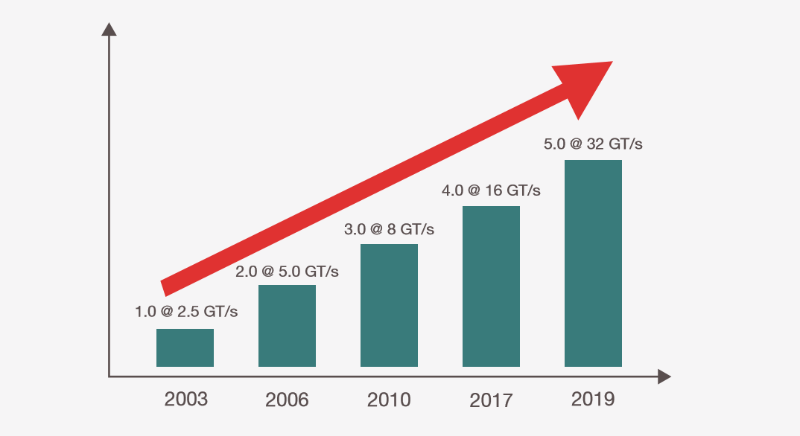

The PCI Special Interest Group (PCI-SIG®) defines specifications and compliance tests that ensure the interoperability of PCIe systems. The PCIe standard evolved from PCIe 1.0, released in 2003 supporting 2.5 gigatransfers per second (GT/s), to PCIe 5.0, released in 2019 supporting 32 GT/s. Figure 1 shows the evolution of the standard and the bandwidth doubling with each generation.

Summary of the Standards

In PCIe 2.0, the bit rate is 5 GT/s, but with the 20% performance overhead of the 8b/10b encoding scheme, the delivered bandwidth is 4 Gb/s. PCIe 3.0 and later versions use more efficient 128b/130b encoding, whittling the overhead down to a modest 1.5%. By removing this overhead, the interconnect bandwidth doubled to 8 Gb/s with the implementation of the PCIe 3.0 specification while preserving compatibility with version 2.0 software and mechanical interfaces. With full backward compatibility, PCIe 3.0 provides the same topologies and channel reach for client and server configurations as in PCIe 2.0.

PCIe 1.x and 2.x cards seamlessly plug into PCIe 3.0-capable slots, and vice versa, operating at the highest performance levels supported by those configurations. The PCIe 3.0 specifications comprise the Base and Card Electromechanical (CEM) specifications. The electrical section of the PCIe 3.0 Base Specification defines electrical performance at the integrated circuit (IC) level and supports 8 GT/s signaling.

The PCIe 3.0 standard added receiver equalization and transmitter de-emphasis tests, which are critical for success at 8 GT/s and above. Equalization can occur at the transmitter, the receiver, or both. PCIe 1.x and PCIe 2.x specify a simple form of equalization called transmitter de-emphasis. De-emphasis reduces the low-frequency energy seen by the receiver. Equalization reduces the effects of greater channel loss at high frequencies. Receiver equalization implementation requires various types of algorithms; the two most common are linear and decision feedback (DFE). Transmitter de-emphasis equalization occurs at the transmitter, while DFE equalization occurs at the receiver. Receiver equalization at the receiver can also include continuous-time linear equalization (CTLE) in combination with the DFE.

The PCIe 4.0 standard (Gen 4) debuted in 2017, seven years after completion of PCIe 3.0. Compared with its predecessor, Gen 4 doubled the data rate from 8 to 16 Gb/s. Gen 4 architecture is compatible with prior generations of the technology, from software to clocking architecture to mechanical interfaces. From a protocol and encoding standpoint, Gen 4 looks a lot like PCIe Gen 3, sharing many elements in common, including 128/130-bit encoding. At first glance, Gen 4 has more in common with Gen 3 than Gen 3 does with Gen 2. But when you increase the speed of the device, you are automatically sending higher frequencies through the same channel. Insertion loss, or attenuation caused by resistance in the link during electrical signal transmission, increases with higher frequency rates.

The PCI-SIG released the PCIe 5.0 specification in May 2019. The fast release of the Gen 5 interface, completed in less than two years, was a welcome change after the seven-year wait for PCIe 4.0. PCIe 5.0 doubles the transfer rate once again, reaching 32 GT/s while maintaining low power and backward compatibility with previous generations. Gen 5 promises up to 128 GB/s of throughput via an x16 configuration, enabling 400GE speeds in the data center. Together, 400GE speeds and PCIe 5.0 enable applications such as artificial intelligence (AI), machine learning, gaming, visual computing, storage, and networking. These advances allow users to drive innovation in 5G, cloud computing, and hyperscale data centers.

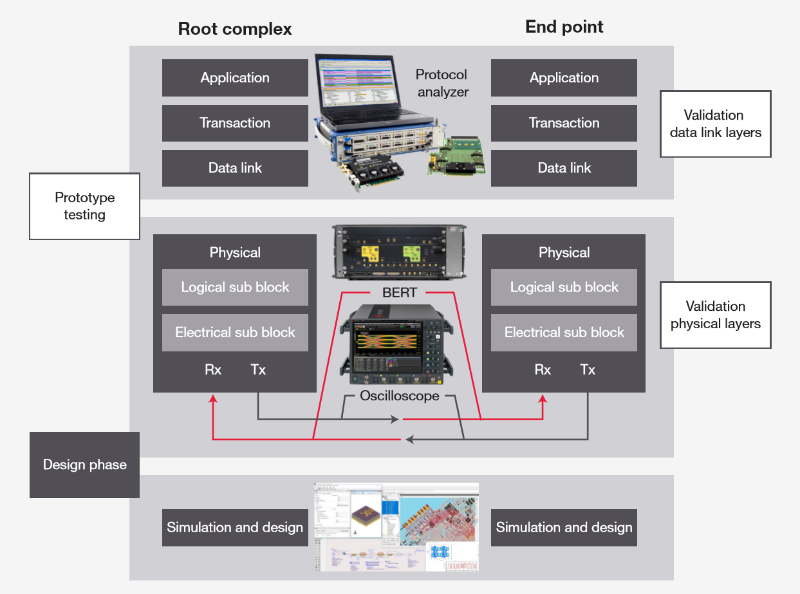

Different types of test equipment must perform different categories of tests from design to first prototypes (Refer to Figure 2):

Oscilloscopes validate physical-layer transmitter (Tx) test.

Bit error ratio testers (BERTs) validate physical-layer receiver (Rx) test.

Protocol analyzers validate data link layers.\

Each generation of the PCIe standard doubled the data transfer rate and increased the complexity of test. Regardless of which generation of the standard you are working on, you need a test solution approved by PCI-SIG to ensure that your products comply with the standard and get to market faster. Keysight provides a total-solution approach to test all generations of the PCIe standard, so you can focus on your next design, rather than spending time learning the details of the test procedures and requirements. Visit PCI Express solutions to learn more.