PAM4 And How Forward Error Correction (FEC) Produces Relief - And New Problems

Forward Error Correction [1] is becoming ubiquitous in the data-center. Not only in 400G links, where SNR requirements to achieve error-free transmission using PAM4 modulation cannot be met anymore, but also for 100G links, where so-called multi-source agreements [2] rely on FEC to reduce the cost of transceivers by relaxing the requirement on the components.

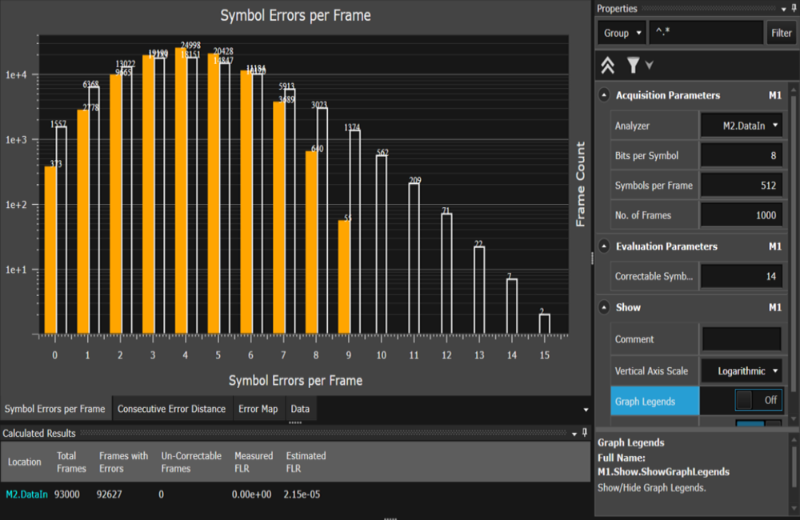

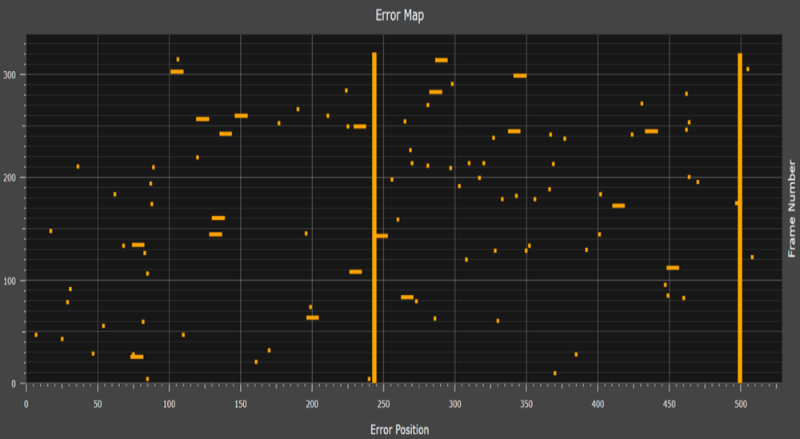

The testing of FEC-enabled systems comes with new challenges: Layer 1 test recommendations as defined by the IEEE aren’t limited to the Bit-Error-Rate measurement anymore: The Frame Loss Ratio, i.e. the system performance after FEC decoding, must also be taken into consideration [3]. This is particularly challenging as FEC encoding & decoding processes involve steps such as scrambling and striping which are very difficult to preserve or reproduce during a stress test for instance. Another fundamental issue of FEC-enabled systems testing is the necessity to characterize and understand the error mechanisms, such as bursts or systematic errors, that can affect the system margin. Generally, this kind of information cannot be provided by the FEC engine of the device under test.

A series of new functionalities has been introduced in Keysight’s M8000 BERT platform to help engineers address these new challenges: The FEC-encoding feature available on the M8040A platform enables the testing of 100GBASE-DR[4] transceivers or PHY chip in presence of physical impairments like jitter, noise and CMI, but also of logical errors such as Bit Interleaved Parity error inserted after or before FEC encoding. Moreover, the M8070EDAB Error Distribution Analysis package offers features like burst mechanism analysis, frame loss ratio estimation and error mapping. It can be used to estimate the system FEC margin or find the root cause of systematic errors by exploring the error map.

References & links

- Forward error correction solutions white paper

- www.cwdm4-msa.org,, www.psm4.org/, www.cwdm4-msa.org,

- IEEE 802.3bs , clause 124

- IEEE 802.3cd , clause 140